- Flex PCB Blog

- PCB Assembly Blog

- FPC Research Blog

- Preparation of FPC based on ultrasonic spraying method_4_Experimental Results

- Preparation of FPC based on ultrasonic spraying method_3_Experimental Procedure

- Preparation of FPC based on ultrasonic spraying method_2_Experimental Platform and Principle

- Preparation of FPC based on ultrasonic spraying method_1_abstract

- Research on Layout Design Method of Ultra-thin FPC_4_Analysis of Layout Design Methods

- Research on Layout Design Method of Ultra-thin FPC_3_Analysis of Layout Design Methods

- Research on Layout Design Method of Ultra-thin FPC_2_Analysis of Layout Design Methods

- Research on Layout Design Method of Ultra-thin FPC_1_introduction

- Research progress on polyimide FPC_2_the field of FPC

- Research progress on polyimide FPC_1_Introduction

- Analysis of Vibration Characteristics of FPCBs _4_Summary

- Analysis of Vibration Characteristics of FPCBs _3_Finite Element Analysis

- Analysis of Vibration Characteristics of FPCBs _2_Theory of Vibration Analysis

- Analysis of Vibration Characteristics of FPCBs Under Random Vibration_1_Introduction

- Design Methods for FPCBs_5_Practical Application

- Design Methods for FPCBs_4_Electrical Circuit Design and Examples

- Design Methods for FPCBs_3_Structure Design Method and Examples

- Design Methods for FPCBs_2_Component Selection Methodology and Examples.

- Research on Design Methods for FPCBs

- Application of MPW technique for FPCBs _4_Summary

- Application of MPW technique for FPCBs_3_Experimental results

- Application of MPW technique for FPCBs_2_Experimental setup

- Application of MPW technique for FPCBs_1_Principle of MPW

- Application of FPCB in PC motherboards_4_ Results and discussion

- Application of FPCB in PC motherboards_3_ Numerical analysis

- Application of FPCB in PC_2_ Experimentation

- Application of FPCB in PC motherboards

- A Bus Planning Algorithm for FPC Design _4_Experimental result

- A Bus Planning Algorithm for FPC Design _3_Proposed Algorithm

- A Bus Planning Algorithm for FPC Design _2_Preliminaries

- A Bus Planning Algorithm for FPC Design _1_Introduction

A Bus Planning Algorithm for FPC Design in Complex Scenarios_4_Experimental result

IV. Experimental result

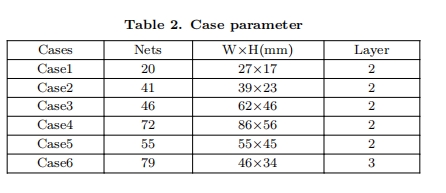

The simulation is implemented in C++ and runs on an Intel Windows machine with 2.69 GHz frequency and 16GB RAM. All simulation scenarios are derived by the actual industry and their parameters are shown in Table 2, W×H is the width and height of the cases.Our router uses congestion based A* PathFinder and the actual routing results need to be further processed, but it does not affect the effectiveness of our al- gorithm. The free-routing also routes the GND net while our method does not consider this issue, but the GND net is usually short and gathers together, so it will only take a little time and have no other impact.

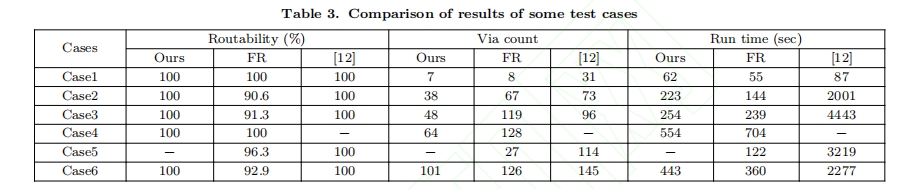

The experimental comparison in this paper is the current advanced open-source router free-routing and the improved integrated 3D A* algorithm. The comparison results are shown in Table 3, where FR rep- resents the method of free-routing. The time used in our method is the sum of routing time and SA iteration time. Wire length in FPC is not suitable as a comparis- on indicator because the routing algorithm based on the minimum line length often causes a lot of congestion in the channel, so it did not participate in the comparison Case 5 cannot be normally executed because there is an irresolvable intersection in the channel; the engineer also solves this problem by punching in the channel. It can be seen from the results that the number of vias can be greatly reduced by using the bus planning proposed in this paper, not only does the algorithm provide a better layer assignment, but also because there is no cross within the channel. Since the heuristic algorithm has a fixed iteration round, the method we proposed is still time-consuming on smaller cases. FR is more time-consuming than our algorithm in some cases, this is because these cases have large channels, which takes a lot of time to solve the cross problem within the channels. As a result, our proposed method has the least number of vias. The method in Ref. takes a long time be- cause the search area is too large, and Case 4 is too large to complete routing. uses the largest number of vias because of its strong detour capacity, and the same with FR, the vias are mostly concentrated in the channel area, which indicates that the current automat- ic routing framework for PCB is difficult to adapt to the channel of the FPC.

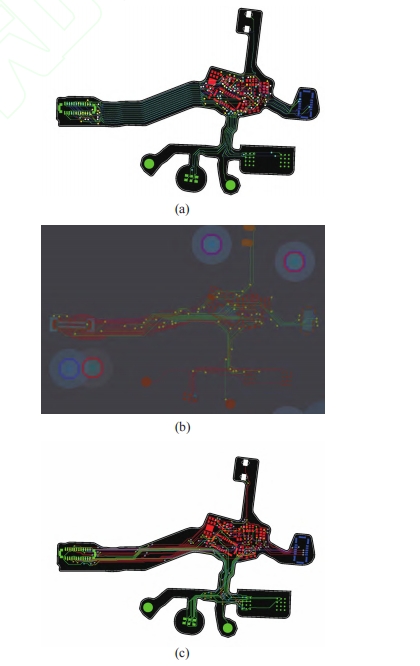

the authors also compare the performance with FR. In particular, the speed of the proposed method is faster than FR, where there this may involvem three reasons. First is the version of FR; their use is backward, which may lead to different efficiency. The second is their method has a very strong detour capacity, which leads to more serious crossovers in FPC channels. The third is the routing strategy in FR may be more suitable for FPC compared with Ref.[12].Fig.10 shows the routing results of the above three methods on case 6, one can find that our proposed method strictly guarantees the constraint of the channel while FR and the method proposed in Ref.punch a lot of vias in the channel, which is not applicable in actual manual routing.

Fig.10. Compared with case 6, a is our result, b and c are FR and [12] result.

V. Conclusion

In this paper, a bus planning algorithm is proposed considering FPC topology. The planning algorithm we proposed fully utilizes the characteristics of FPC and ensures special constraints. The experiments are conducted on industrial FPC cases. The results demonstrate that our algorithm improves routability,reduces via count and has an acceptable run time compared with state-of-the-art methods.With the development of electronic products, FPC will become increasingly popular, and will also perform expanding number of novel circuit functions. In this manner, FPC will become closer to PCB in function and scale, which is a new challenge to FPC automation design. The FPC problems such as differential pairs can be selected as our research directions.